# **Advance Information**

## INTELLIGENT PERIPHERAL CONTROLLER

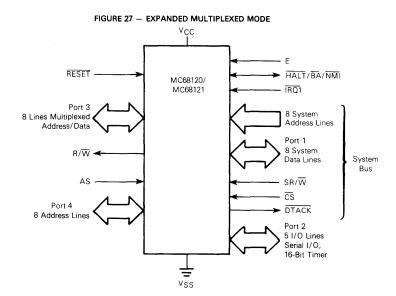

The MC68120/MC68121 Intelligent Peripheral Controller (IPC) is a general purpose, mask programmable peripheral controller. The IPC provides the interface between an M68000 or M68000 Family microprocessor and the final peripheral devices through a system bus and control lines. System bus data is transferred to and from the IPC via dual-port RAM while the software utilizes the semaphore registers to control RAM tasking or any other shared resource. Multiple operating modes range from a single chip mode with 21 I/O lines and 2 control lines to an expanded mode supporting an address space of 64K bytes. The MC68120 has 2K bytes of on-chip ROM to make full use of all operating modes. The MC68120 the absence of on-chip ROM.

A serial communications interface, 16-bit timer, dual-ported RAM and semaphore registers are available for use by the IPC in all operating modes.

- System Bus Compatible with the Asynchronous M68000 Family

- System Bus Compatible with the MC6809 and Other M6800 Family Processors/Peripherals

- Local Bus Allows Interface with all M6800 Peripherals

- MC6801 Source and Object Code Compatible

- Upward Compatible with MC6800 Source and Object Code

- 2048 Bytes of ROM (MC68120 Only)

- 128 Bytes of Dual-Ported RAM

- Multiple Operation Modes Ranging from Single Chip to Expanded, with 64K Byte Address Space

- Six Shared Semaphore Registers

- 21 Parallel I/O Lines and 2 Handshake Lines (5 I/O Lines on MC68121)

- Serial Communications Interface (SCI)

- 16-Bit Three-Function Timer

- 8-Bit CPU and Internal Bus

- Halt/Bus Available Capability Control

- 8×8 Multiply Instruction

- TTL Compatible Inputs and Outputs

- External and Internal Interrupts

|              | GENERIC INFOR<br>(T <sub>A</sub> = 0°C to |                          |

|--------------|-------------------------------------------|--------------------------|

| Package Type | Frequency (MHz)                           | Generic Number           |

| Ceramic      | 1.0                                       | MC68120L1 (Unicorn ROM)  |

| L Suffix     | 1.0                                       | MC68121L                 |

|              | 1.25                                      | MC68120L1-1 (Unicorn ROM |

|              | 1.25                                      | MC68121L-1               |

This document contains information on a new product. Specifications and information herein are subject to change without notice.

# MC68120 MC68121

## **HMOS**

(HIGH-DENSITY N-CHANNEL SILICON-GATE)

## INTELLIGENT PERIPHERAL CONTROLLER

| PIN ASS               | IGNMENT               |

|-----------------------|-----------------------|

| Vss C1 •              | 480 RESET             |

|                       | 47 <b>D</b> P24       |

| HALT/<br>BA/NMIC3     | 46 <b>]</b> P23       |

| E C4                  | 45 <b>D</b> P22       |

| SR/₩ <b>0</b> 5       | 44 P21                |

| DTACK C               | 43 <b>D</b> P20       |

| <u>ट</u> ड <b>ट</b> 7 | 42 <b>D</b> SC2       |

| SA7 🗖 8               | 41 <b>]</b> SC1       |

| SA6 🗖 9               | 40 P30                |

| SA5 🖸 10              | 39 <mark>1</mark> P31 |

| SA4 🗖 11              | 38 <b>0</b> P32       |

| VCC <b>[</b> 12       | 37 <b>D</b> P33       |

| SA3 🗖 13              | 36 <b>D</b> P34       |

| SA2 🗖 14              | 35 <b>1</b> P35       |

| SA1 🗖 15              | 34 🗖 P36              |

| SA0 🗖 16              | 33 <mark>1</mark> P37 |

| SD0 🚺 17              | 32 <b>]</b> P40       |

| SD1 🗖 18              | 31 <b>D</b> P41       |

| SD2 🗖 19              | 30 <b>D</b> P42       |

| SD3 🗖 20              | 29 <b>0</b> P43       |

| SD4 🖸 21              | 28 <b>2</b> P44       |

| SD5 <b>C</b> 22       | 27 <b>]</b> P45       |

| SD6 🖸 23              | 26 <b>0</b> P46       |

| SD7 <b>Q</b> 24       | 25 P47                |

|                       |                       |

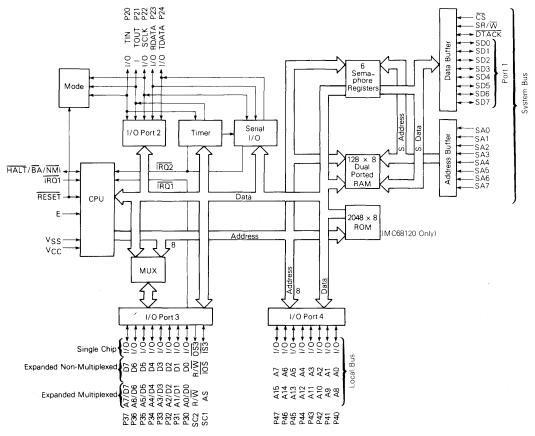

MC68120/MC68121 INTELLIGENT PERIPHERAL CONTROLLER - BLOCK DIAGRAM

## MAXIMUM RATINGS

| Rating                      | Symbol           | Value        | Unit |

|-----------------------------|------------------|--------------|------|

| Suppiy Voltage              | Vcc              | -0.3 to +7.0 | V    |

| Input Voltage               | Vin              | -0.3 to +7.0 | V    |

| Operating Temperature Range | TA               | 0 to 70      | °C   |

| Storage Temperature Range   | T <sub>stg</sub> | -55 to +150  | °C   |

## THERMAL CHARACTERISTICS

| Characteristic     | Symbol | Value | Rating |

|--------------------|--------|-------|--------|

| Thermal Resistance |        |       |        |

| Ceramic Package    | θια    | 50    | °C/W   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation it is recommended that V<sub>in</sub> and V<sub>out</sub> be constrained to the range V<sub>SS</sub> ≤ (V<sub>in</sub> or V<sub>out</sub> ≤ VCc.) Unused inputs must always be tied to an

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or VCC).

## POWER CONSIDERATIONS

The average chip-junction temperature, TJ, in °C can be obtained from:

$T_J = T_A + (P_D \bullet \theta_{JA})$

Where:

T<sub>A</sub> ≡ Ambient Temperature, °C

$\theta_{JA} = Package Thermal Resistance, Junction-to-Ambient, °C/W$

PD≡PINT+PPORT

PINT≡ICC×VCC, Watts – Chip Internal Power

PPORT=Port Power Dissipation, Watts - User Determined

For most applications PPORT PINT and can be neglected. PPORT may become significant if the device is configured to drive Darlington bases or sink LED loads.

An approximate relationship between PD and TJ (if PPORT is neglected) is:

$P_{D} = K + (T_{J} + 273^{\circ}C)$

(2)

(1)

Solving equations 1 and 2 for K gives:

$K = P_{D} \bullet (T_{A} + 273^{\circ}C) + \theta_{J}A \bullet P_{D}^{2}$

Where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring PD (at equilibrium) for a known TA. Using this value of K the values of PD and TJ can be obtained by solving equations (1) and (2) iteratively for any value of TA.

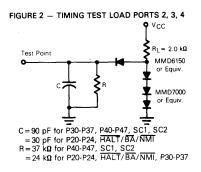

DC LOCAL BUS ELECTRICAL CHARACTERISTICS ( $V_{CC}$  = 5.0 Vdc ±5%,  $V_{SS}$  = 0,  $T_A$  = 0° to 70°C unless otherwise noted) (Refer to Figures 1 and 2)

Max Unit Min Characteristic Symbol Тур F V<u>CC</u>-0.75 v Input High Voltage VEIH Vcc Input Low Voltage Ε VEIL VSS-0.3 VSS+0.6 V Input High Voltage RESET VSS + 4.0 Vcc \_ ViH v Other Inputs\* VSS+2.0 Vcc All Inputs\* VSS-0.3 Input Low Voltage VIL  $V_{SS} + 0.8$ v -Input Load Current lin 05 mΑ Port 4 (Vin = 0 to 2.4 V) Input Leakage Current lin 1.5 2.5 μA SCI, HALT/NMI, IRQ1, RESET  $(V_{in} = 0 \text{ to } 5.25 \text{ V})$ Three-State (Off State) Input Current ITSI 2.0 10 *"*Δ  $(V_{in} = 0.5 \text{ to } 2.4 \text{ V})$ SD0-SD7, P20-P24, P30-P37 Output High Voltage  $(I_{load} = -65 \mu A, V_{CC} = min)$ P40-P47, SC1, SC2 VSS+2.4 ∨он v  $(I_{load} = -100 \,\mu\text{A}, V_{CC} = \text{min})$ Other Outputs V<sub>SS</sub>+2.4 \_ Output Low Voltage Vol VSS+0.5 v \_ \_  $(I_{load} = 2.0 \text{ mA}, V_{CC} = \text{min})$ All Outputs Internal Power Dissipation (measured at  $T_{\Delta} = 0^{\circ}$ C) PINT 1200 mW \_ \_ Input Capacitance 60.0 F ---рF  $(V_{in} = 0, T_A = 25^{\circ}C, f_0 = 1.0 \text{ MHz})$ P30-P37, P40-P47, SC1 12.5 Cin \_ \_ Other Inputs \_ 10.0

\* Except Mode Programming Levels; See Figure 29.

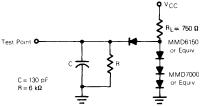

FIGURE 1 - CMOS LOAD

3-704

## DC SYSTEM BUS ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub>=5.0 Vdc ±5%, V<sub>SS</sub>=0, T<sub>A</sub>=70°C unless otherwise noted) (Refer to Figure 3)

|                                 | Characteristic                                       |                        | Symbol | Min                   | Тур | Max                  | Unit |

|---------------------------------|------------------------------------------------------|------------------------|--------|-----------------------|-----|----------------------|------|

| Input High Voltage              | CS, DTACK, S                                         | SAO-SA7, SDO-SD7, SR/W | ⊻н     | V <sub>SS</sub> + 2.0 |     | Vcc                  | V    |

| Input Low Voltage               | CS, DTACK, S                                         | SAO-SA7, SDO-SD7, SR/W | VIL    | V <sub>SS</sub> -0.3  | -   | VSS+0.8              | V    |

| Output High Voltage (ILoad = -4 | $00 \mu\text{A}, \text{V}_{\text{CC}} = \text{min})$ | DTACK, SD0-SD7         | Vон    | $V_{SS} + 2.4$        |     | -                    | V    |

| Output Low Voltage (ILoad = 5.3 | mA, V <sub>CC</sub> = min)                           | DTACK, SD0-SD7         | VOL    | -                     | -   | V <sub>SS</sub> +0.5 | V    |

## FIGURE 3 - TIMING TEST LOAD SD0-SD7, DTACK

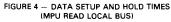

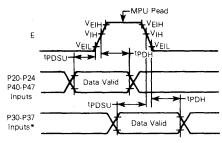

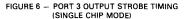

## PERIPHERAL PORT TIMING (Refer to Figures 4 through 7)

| Characteristics                                                                 | Symbol            | Min | Max | Unit |

|---------------------------------------------------------------------------------|-------------------|-----|-----|------|

| Peripheral Data Setup Time                                                      | <sup>t</sup> PDSU | 200 |     | ns   |

| Peripheral Data Hold Time                                                       | <sup>t</sup> PDH  | 200 | ·   | ns   |

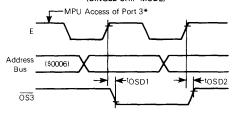

| Delay Time, Enable Positive Transition to OS3 Negative Transition               | tOSD1             | _   | 350 | ns   |

| Delay Time, Enable Positive Transition to OS3 Positive Transition               | tOSD2             | -   | 350 | ns   |

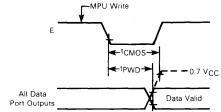

| Delay Time, Enable Negative Transition to Peripheral Data Valid (Ports 2, 3, 4) | <sup>t</sup> PWD  | -   | 350 | ns   |

| Delay Time, Enable Negative Transition to Peripheral CMOS Data Valid            | <sup>t</sup> CMOS | _   | 2.0 | μs   |

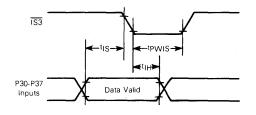

| Input Strobe Pulse Width                                                        | tPWIS             | 200 | -   | ns   |

| Input Data Hold Time                                                            | ΫН                | 60  | -   | ns   |

| Input Data Setup Time                                                           | tis               | 20  | -   | ns   |

| Input Capture Pulse Width (Timer Function)                                      | <sup>t</sup> PWIC | 2   | -   | Ecyc |

\* Port 3 Non-Latched Operation (LATCH ENABLE=0)

\* Access matches Output Strobe Select (OSS=0, a read; OSS=1, a write) FIGURE 5 – DATA SETUP AND HOLD TIMES (MPU WRITE LOCAL BUS)

Notes:

1. 10 k Pullup resistor required for Port 2 to reach:0.7 VCC

2. Not applicable to P21

3. Port 4 cannot be pulled above V<sub>CC</sub>

FIGURE 7 — PORT 3 LATCH TIMING (SINGLE CHIP MODE)

Note: Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted.

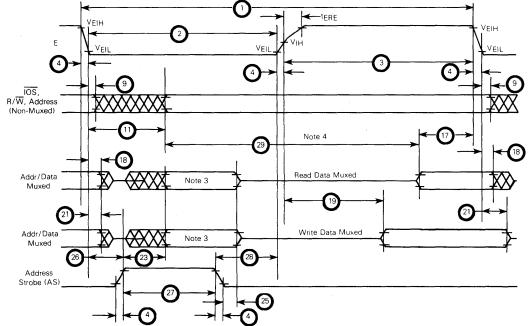

| Ident. | Characteristics              | Symbol              | MC68120/<br>MC68121 |      | MC68120-1/<br>MC68121-1 |      | Unit |

|--------|------------------------------|---------------------|---------------------|------|-------------------------|------|------|

| Number |                              |                     | Min                 | Max  | Min                     | Max  |      |

| 1      | Cycle Time                   | t <sub>cyc</sub>    | 1.0                 | 2.0  | 0.8                     | 2.0  | μs   |

| 2      | Pulse Width, E Low           | PWEL                | 430                 | 1000 | 360                     | 1000 | ns   |

| 3      | Pulse Width, E High          | PWEH                | 450                 | 1000 | 360                     | 1000 | ns   |

| 4      | Clock Rise and Fall Time     | t <sub>r</sub> , tf | -                   | 25   | -                       | 25   | ns   |

| 9      | Non-Muxed Address Hold Time  | <sup>t</sup> AH     | 20                  | -    | 20                      | -    | ns   |

| 11     | Address Delay From E Low     | tAD                 |                     | 260  | _                       | 220  | ns   |

| 17     | Read Data Setup Time         | <sup>t</sup> DSR    | 80                  | -    | 70                      | -    | ns   |

| 18     | Read Data Hold Time          | <sup>t</sup> DHR    | 10                  | -    | 10                      | -    | - ns |

| 19     | Write Data Delay Time        | tDDW                |                     | 225  | -                       | 200  | ns   |

| 21     | Write Data Hold Time         | <sup>t</sup> DHW    | 20                  | -    | 20                      | -    | ns   |

| 23     | Muxed Address Delay from AS  | <sup>t</sup> ADM    | -                   | 90   | -                       | 80   | ns   |

| 25     | Muxed Address Hold Time      | <sup>t</sup> AHL    | 20                  | 110  | 20                      | 110  | ns   |

| 26     | Delay Time E to AS Rise      | tASD                | 100                 | -    | 80                      | -    | ns   |

| 27     | Pulse Width, AS High         | PWASH               | 220                 | -    | 170                     | -    | ns   |

| 28     | Delay Time AS to E Rise      | <b>tASED</b>        | 100                 |      | 80                      | -    | ns   |

| 29     | Usable Access Time (Note 4)  | tACC                | 570                 | -    | 435                     | ·    | ns   |

|        | Enable Rise Time Extended    | <sup>t</sup> ERE    | -                   | 80   | -                       | 80   | ns   |

|        | Processor Control Setup Time | <b>t</b> PCS        | 200                 | - '  | 200                     | -    | ns   |

|        | Processor Control Hold Time  | <sup>t</sup> PCH    | 20                  | 40   | 20                      | 40   | ns   |

#### LOCAL BUS TIMING (See Notes 1 and 2)

## NOTES

- Voltage levels shown are VL≤0.5 V, VH≥2.4 V, unless otherwise specified.

Measurement points shown are 0.8 V and 2.0 V, unless otherwise specified.

Address valid on the occurrence of the latest of 11 or 23.

- 4. Usable access time is computed by: 1 (4 + 11 + 17).

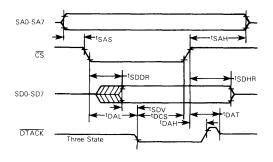

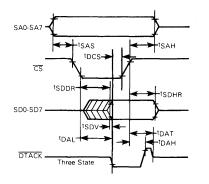

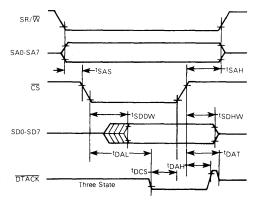

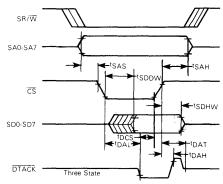

## ASYNCHRONOUS SYSTEM BUS TIMING (Refer to Figures 9, 10, 11 and 12)

| Characterisic                        | Symbol            | Min | Тур | Max                          | Unit |

|--------------------------------------|-------------------|-----|-----|------------------------------|------|

| Cycle Time                           | tcyc              | 0.8 | -   | 2.0                          | μs   |

| System Address Setup                 | tsas              | 30  | -   | _                            | ns   |

| System Address Hold                  | <sup>t</sup> SAH  | 0   | -   | -                            | ns   |

| System Data Delay Read               |                   |     |     | 0.3+1.5                      |      |

| Semaphore                            | tSDDR             | 0.3 | -   | t <sub>cyc</sub> *           | μs   |

| RAM                                  | tSDDR             |     | 315 | _                            | ns   |

| System Data Valid                    | tSDV              | 0   | -   | _                            | ns   |

| System Data Hold Read                | <sup>t</sup> SDHR | 0   | -   | 100                          | ns   |

| System Data Delay Write<br>Semaphore | tSDDW             |     | _   | ••                           | ns   |

| RAM                                  | tSDDW             | -   | -   | 60                           | ns   |

| System Data Hold Write               | tSDHW             | 0   | -   |                              | ns   |

| Data Acknowledge<br>Semaphore        | <sup>t</sup> DAL  | 0.5 | _   | 0.5+1.5<br><sup>t</sup> cyc* | μs   |

| RAM                                  | <sup>t</sup> DAL  |     | 315 | -                            | ns   |

| Data Acknowledge High                | <sup>t</sup> DAH  |     |     | 60                           | ns   |

| Data Acknowledge Three-State         | <sup>t</sup> DAT  | -   |     | 90                           | ns   |

| Data Acknowledge Low to CS High      | tDCS              | 60  | -   | _                            | ns   |

\* Actual value dependent upon clock period.

\* \* Data need not be valid on write to Semaphore Registers.

## FIGURE 9 - ASYNCHRONOUS READ OF SEMAPHORE REGISTER

FIGURE 11 - ASYNCHRONOUS READ OF RAM

Note: Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted.

## FIGURE 10 - ASYNCHRONOUS WRITE OF SEMAPHORE REGISTER

#### FIGURE 12 - ASYNCHRONOUS WRITE OF RAM

3

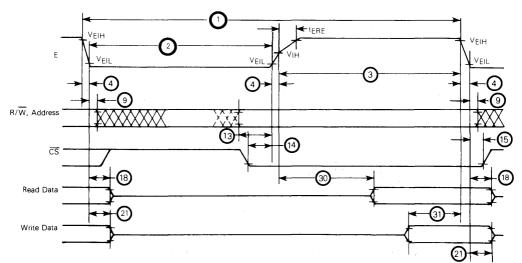

## SYNCHRONOUS SYSTEM BUS TIMING (See Notes 1 and 2)

| Ident<br>Number | Characteristic                  | Symbol              | MC68120/<br>MC68121 |      | MC68120-1<br>MC68121-1 |          | Unit |  |

|-----------------|---------------------------------|---------------------|---------------------|------|------------------------|----------|------|--|

| Number          |                                 |                     | Min                 | Max  | Min                    | Max      |      |  |

| 1               | Cycle Time                      | tcyc                | 1.0                 | 10   | 0.80                   | 10       | μs   |  |

| 2               | Pulse Width, E Low              | PWEL                | 430                 | 9500 | 360                    | 9500     | ns   |  |

| 3               | Pulse Width, E High             | PWEH                | 450                 | 9500 | 360                    | 9500     | ns   |  |

| 4               | Clock Rise and Fall Time        | t <sub>r</sub> , tf |                     | 25   | -                      | 25       | ns   |  |

| 9               | Address Hold Time               | <sup>t</sup> AH     | 10                  | -    | 10                     | -        | ns   |  |

| 13              | Address Setup Time Before E     | tAS                 | 80                  | -    | 70                     | <u> </u> | ns   |  |

| 14              | Chip Select Setup Time Before E | tCS                 | 80                  | . —  | 70                     | . –      | ns   |  |

| 15              | Chip Select Hold Time           | tCH                 | 10                  | -    | 10                     | -        | ns   |  |

| 18              | Read Data Hold Time             | <sup>t</sup> DHR    | 30                  | 100  | 30                     | 85       | ns   |  |

| 21              | Write Data Hold Time            | <sup>t</sup> DHW    | 10                  | -    | 10                     | -        | ns   |  |

| 30              | Output Data Delay Time          | <sup>t</sup> DDR    | -                   | 290  | -                      | 250      | ns   |  |

| 31              | Input Data Setup Time           | tDSW                | 165                 | -    | 120                    |          | ns   |  |

|                 | Clock Enable Rise Time Extended | tere                | -                   | 80   | -                      | 80       | ns   |  |

## FIGURE 13 - SYNCHRONOUS SYSTEM BUS TIMING

Notes:

Voltage levels shown are VL≤0.5 V, VH≥2.4 V, unless otherwise specified.

Measurement points shown are 0.8 V and 2.0 V, unless otherwise specified.

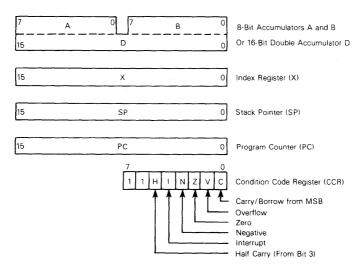

### INTRODUCTION

The MC68120/MC68121 is an 8-bit Intelligent Peripheral Controller (IPC) which can be configured to function in a wide variety of applications. This extraordinary flexibility is provided by its ability to be hardware programmed into eight different operating modes. These operating modes allow the IPC to operate on its local bus and communicate with an external system bus through the internal dual-ported RAM. The operating mode controls the configuration of 18 of the 48 pins on the IPC, the available on-chip resources, the memory map, the location (internal or external) of interrupt vectors, and the type of local bus. The configuration of the remaining 30 pins is not controlled by the operating mode.

The dual-ported RAM provides a vehicle for devices on two separate buses to exchange data without directly affecting the devices on the other bus. The dual-ported RAM is accessible from the MC68120/MC68121 CPU and accessible synchronously or asynchronously to the system bus through Port 1. Semaphore registers are provided as a software tool to arbitrate shared resources such as the dual-ported RAM. The semaphore registers are accessible from both buses in the same way each bus accesses the dual-ported RAM. The remaining ports (2, 3, and 4) are I/O ports. Each port is controlled by its Data Direction Register. The CPU has direct access to the port pins of each port through its Data Register. Port pins are labeled as P<sub>ij</sub> where i identifies one of three ports and j indicates the particular bit. Port 2 is a 5-bit port which may be configured for I/O or for use of the on-chip timer and Serial Communications Interface ISCI). Ports 3 and 4 may be used as 16 bits of I/O or may form a local address and data bus with control lines allowing communications with external memory and peripherals.

The IPC contains an enhanced M6800 MPU with additional capabilities and greater throughput. It is upward source and object code compatible with the MC6800 and directly compatible with the MC6801. The programming model is depicted in Figure 14, where accumulator D is a concatenation of accumulators A and B.

The MC68121 has all of the features of the MC68120 with the exception of on-chip ROM. Thus the MC68121 normally operates in the modes utilizing external ROM (modes 2 and 3). Therefore, modes 0, 1, 4, 5, 6 and 7 should not be used.

#### FIGURE 14 - PROGRAMMING MODEL

## DUAL-PORTED RAM AND SEMAPHORE REGISTERS

The dual-ported RAM may be accessed from both the MC68120/MC68121 CPU and the external system bus. The six semaphore registers are tools provided for the programmer's use in arbitrating simultaneous accesses of the same resource.

For the internal CPU, the dual-ported RAM is located from \$0080 through \$00FF in all modes except 3 and 4. In mode 3,

the dual-ported RAM has been relocated in high memory from \$C080 through \$C0FF thus allowing use of direct addressing mode on external memory/peripherals. Note that no direct addressing of internal control registers is possible in mode 3. In mode 4, the internal RAM is not fully decoded and appears in locations \$XX80 through \$XXFF. From the external system bus, the dual-ported RAM is found in locations %1000000-11111111, as shown below in Table 1.

|   | TABLE 1 | LOCATION | OF SEMAPHOR | RE REGISTERS AND | DUAL-PORTED RAM |

|---|---------|----------|-------------|------------------|-----------------|

| 1 |         |          |             |                  |                 |

| System Bus Address<br>(SA7-SA0) |                         |         |

|---------------------------------|-------------------------|---------|

| %0000 0000 - 0001 0110          | Reserved                |         |

|                                 | Internal Registers      | \$00-16 |

| 0001 0111 - 0001 1100           | Semaphore Registers     | 17-1C   |

| 0001 1101 - 0111 1111           | Reserved                | 1D-1F   |

|                                 | External Mem./Unusable* | 20-7F   |

| 1000 0000 - 1111 1111           | Dual-Ported RAM         | 80-FF   |

% = Binary; \$ = Hexadecimal \* Mode Dependent

The reserved memory areas %0-0001 0110 and %0001

1101-%0111 1111 cannot be written to from the System bus. If read from the System bus these memory locations return a value of \$FF. The dual-ported RAM is accessed from the external

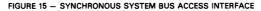

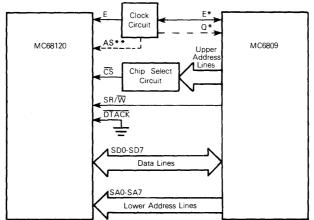

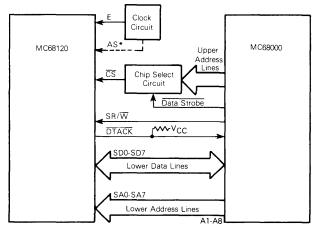

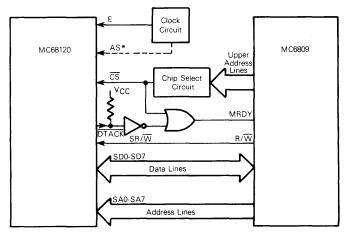

System bus by way of eight address lines (SA0-SA7) and eight data lines (SD0-SD7). Three control lines provide for synchronous or asynchronous access to the dual-ported RAM through Port 1. Figure 15 shows an example of a synchronous interface (using MC6809) and Figure 16 shows an example of an asynchronous interface (using MC68000). The dual-ported RAM is selected in each case by address lines SA0-SA7 and Chip Select (CS) from the system bus. The direction of data transfer is selected by the System Read/Write (SR/ $\overline{W}$ ) line. The Data Transfer Acknowledge (DTACK) signal is the asynchronous handshake required by an MC68000. Refer to DTACK under Functional Pin Description for more information. DTACK can be used to control a Memory Ready signal on the M6800 Family processor where Memory Ready capability is provided (see Figure 17). The latter would allow the M6800 Family processor to run asynchronously with the MC68120/MC68121. It should be noted that if the Memory Ready signal (on M6800 processors) is to be used with the DTACK signal, the system clock must be faster than or equal to the clock driving the IPC. Example clock circuits are shown in Figures 18 and 19.

\* E and Q are inputs for MC6809E

\*\*Only needed in expanded multiplexed modes.

FIGURE 16 - ASYNCHRONOUS SYSTEM BUS INTERFACE

\* Only needed in expanded multiplexed modes.

FIGURE 17 - MEMORY READY - DTACK CONFIGURATION

\* Only needed in expanded multiplexed modes.

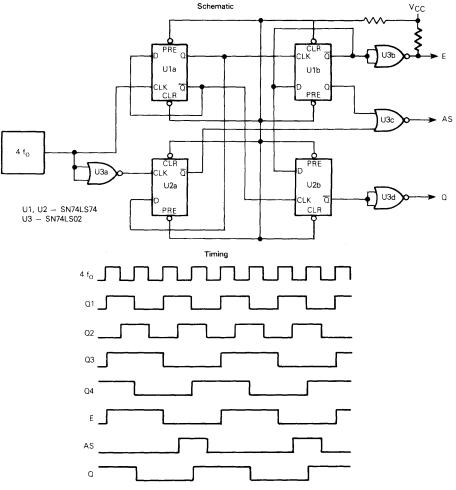

FIGURE 18 - CLOCK CIRCUIT EXAMPLE 1 - SCHEMATIC AND TIMING

The semaphore registers allow arbitration between shared resources, which may be part or all of the dual-port RAM, or a peripheral. The semaphore registers may also be used to indicate that non-reentrant code is in use or that a task is in process or is complete. To prevent the writing or reading of erroneous data from the dual-ported RAM, all simultaneous accesses involving a write to the same byte in the dual-ported RAM should be avoided. The responsibility for mutual exclusion resides in software. The semaphore registers are a convenient means for the software to control the simultaneous accesses involving a write to the dual-ported RAM. Each of the six semaphore registers consist of a semaphore bit (SEM, bit 7) and an ownership bit (OWN, bit 6). The remaining six bits (b0-b5) will read all zeros.

SEMAPHORE REGISTER

| 7   | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|-----|---|---|---|---|---|---|

| SEM | OWN | 0 | 0 | 0 | 0 | 0 | 0 |

The semaphore bits are test and set bits with hardware arbitration during simultaneous accesses. Basically, the semaphore bit is cleared when written and set when read, during a single processor access. This is shown in Table 2.

TABLE 2 - SINGLE PROCESSOR SEMAPHORE BIT TRUTH TABLE

| Original<br>SEM Bit | R/₩ | Data<br>Read | Resulting<br>SEM Bit |

|---------------------|-----|--------------|----------------------|

| 0                   | R   | 0*           | 1                    |

| 1                   | R   | 1*           | . 1                  |

| 0                   | W   | _            | 0                    |

| 1                   | W   | _            | 0                    |

\*0 - Resource Available

1 - Resource Not Available

FIGURE 19 — CLOCK CIRCUIT EXAMPLE 2 — SCHEMATIC AND TIMING Schematic

The data written is disregarded and the information obtained from the Read may be interpreted as: 0 - resource available; 1 - resource not available. Thus, any write to a semaphore clears the semaphore bit and makes the associated resource "available."

An access where both the IPC and system processors attempt to read or write the same semaphore register simultaneously is a contested access. During a contested access, the hardware decides which processor reads a clear semaphore bit and which reads a set semaphore bit. Table 3 describes contested operation of a semaphore bit.

The IPC always reads the actual semaphore bit; the system processor reads the semaphore bit in all cases except the simultaneous read of a clear semaphore bit. This arbitration during a simultaneous read ensures that only one processor reads a clear bit and therefore controls the resource; that processor is arbitrarily the IPC.

In Table 3, the first four states are considered proper and they occur in correctly written software. The last four states are improper and only exist in improperly written software.

The ownership bit is a read-only bit that indicates which processor sets the semaphore bit. If the semaphore bit is set, the ownership bit indicates which processor set it. If the semaphore bit is not set, the ownership bit indicates which processor last set the semaphore bit; OWN = 0, the other processor set SEM; OWN = 1, this processor set SEM.

The reset state of the semaphore and ownership bits is defined in Table 4. All of the semaphore bits are set after an MC68120/MC68121 reset. The IPC owns all of them except the second semaphore which is owned by the system processor. This configuration should prevent the system processor from reading a clear semaphore and implying the system processor set it when the IPC RESET is held low.

|          |                      | System       |     | IPC          |     |                     |

|----------|----------------------|--------------|-----|--------------|-----|---------------------|

|          | Resulting<br>SEM Bit | Data<br>Read | R/₩ | Data<br>Read | R/W | Original<br>SEM Bit |

|          | 1                    | 1*           | R   | 0*           | R.  | . 0                 |

| DDODED   | 0                    | _            | W   | 1*           | R   | 1                   |

| PROPER   | 0                    | 1*           | R   | _            | W   | 1                   |

|          | 1                    | 1*           | R   | 1            | R   | 1                   |

|          | 0                    | -            | W   | _            | W   | 0                   |

|          | 1                    | -            | W   | 0*           | R   | 0                   |

| IMPROPER | 0                    |              | w   | -            | W   | 1                   |

|          | 1                    | 0*           | R   | -            | W   | 0                   |

TABLE 3 - DUAL PROCESSOR SEMAPHORE BIT TRUTH TABLE

\*0 - Resource Available

1 - Resource Not Available

| TABLE 4 - | RESET | STATE | OF SEM | APHORE | REGISTER |

|-----------|-------|-------|--------|--------|----------|

|           |       |       |        |        |          |

| SEM        | IP IP | C   | Sys | tem |

|------------|-------|-----|-----|-----|

| Reg<br>No. | Sem   | Own | Sem | Own |

| 1          | 1     | 1   | 1   | 0   |

| 2          | 1     | 0   | 1   | 1   |

| 3          | 1     | 1   | 1   | 0   |

| 4          | 11    | 1   | 1   | 0   |

| 5          | 1     | 1   | 1   | 0   |

| 6          | 1     | 1   | 1   | 0   |

## **PROGRAM STORAGE MEMORY - ROM**

The standard MC68120 comes preprogrammed with a monitor in the ROM. Custom programs are placed in ROM by special order (see Appendix A).

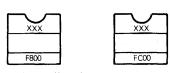

The MC68120 contains 2048 bytes of on-chip, mask programmable read-only memory (ROM) in memory locations \$F800 through \$FFFF. The contents of this ROM allows the IPC to perform a custom function for the user. The interrupt vectors \$FFF0-\$FFFF are decoded to provide vectors at the top of resident ROM. Address \$FFEF is reserved for the checksum value for the ROM. This value is the complement of the "Exclusive OR" of the 2047 bytes of mask programmed ROM. An IPC without ROM is also available as the MC68121. The MC68121 should only be used in modes 2 and 3 to access external ROM after reset.

## FUNCTIONAL PIN DESCRIPTIONS

#### VCC AND VSS

$V_{CC}$  and  $V_{SS}$  provide power and ground to the IPC. The power supply should provide +5 volts ( $\pm5\%$ ) to  $V_{CC}$  and  $V_{SS}$  should be tied to ground. Total power dissipation should not exceed PD milliwatts.

#### RESET

The reset function is used for three purposes. The first is to provide the IPC with an orderly and defined start-up procedure from a powerdown condition. The second is to return to start-up conditions without an intervening powerdown condition. The third is to provide a control signal to latch the operating mode.

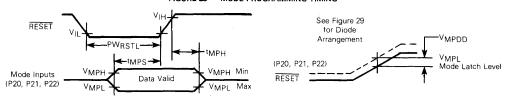

During reset (low logic level on RESET pin), execution of the current instruction is suspended and the CPU enters a "reset state." The register contents are not pushed onto the stack and their contents become undefined during reset. The "reset state" initializes the IPC, as shown in Table 5. On the positive edge of  $\overrightarrow{\text{RESET}}$ , the IPC latches the operating mode from P22, P21 and P20, and then configures Port 3, Port 4, SC1 and SC2. The restart vector is then fetched and transferred to the program counter, then instruction execution begins.

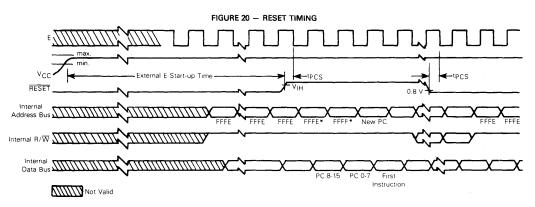

Reset timing is illustrated in Figure 20. The RESET line must be held low for a minimum of three E-cycles for the IPC to complete its entire reset sequence. An external RCnetwork may be used to obtain the required timing.

## ENABLE - E

The E clock input is required for timing to synchronize Data Bus transfers. A "CPU E-cycle" (or bus cycle) consists of a negative half-cycle of E followed by a positive half-cycle. For any given bus cycle, the address is valid during the negative half-cycle of E and the selected device must be enabled to the Data Bus during the next positive half-cycle. The data bus is active only while E is high. It should be noted

| Bits or Registers Effective State                |                                                       |  |  |  |  |  |  |

|--------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|

| CPU I-Bit                                        | set (IRQ1 and IRQ2 disabled)                          |  |  |  |  |  |  |

| NMI Interrupt Latch                              | cleared (NMI disabled)                                |  |  |  |  |  |  |

| Halt Control Bit                                 | cleared (HALT/BA selected)                            |  |  |  |  |  |  |

| All Data Direction Registers                     | cleared                                               |  |  |  |  |  |  |

|                                                  | cleared                                               |  |  |  |  |  |  |

| SCI Rate and Mode Control Register               |                                                       |  |  |  |  |  |  |

| Receive Data Register                            | cleared                                               |  |  |  |  |  |  |

| Timer Control and Status Register                | cleared                                               |  |  |  |  |  |  |

| Free Running Counter                             | cleared                                               |  |  |  |  |  |  |

| Buffer for LSB of Counter                        | cleared                                               |  |  |  |  |  |  |

| Port 3 Control and Status Register               | cleared                                               |  |  |  |  |  |  |

| Port 2, 3, 4 Data Registers                      | undefined after Power-up Reset; and not changed after |  |  |  |  |  |  |

|                                                  | Reset                                                 |  |  |  |  |  |  |

| SCI Transmit/Receive Control and Status Register | Preset to \$20                                        |  |  |  |  |  |  |

| Output Compare Register                          | Preset to \$FFFF                                      |  |  |  |  |  |  |

| Semaphore Bits                                   | Preset to 1's                                         |  |  |  |  |  |  |

| Ownership Bit of Semaphore Register 2            | Preset to System Ownership                            |  |  |  |  |  |  |

| All other Ownership Bits                         | Preset to IPC Ownership                               |  |  |  |  |  |  |

| All Ports 2 and 3 Lines                          | High Impedance (inputs)                               |  |  |  |  |  |  |

| All Port 4 Lines                                 | High Impedance (inputs) with pullup resistors         |  |  |  |  |  |  |

| SC1*                                             | High Impedance with pullup resistors                  |  |  |  |  |  |  |

| SC2                                              | Active High                                           |  |  |  |  |  |  |

#### TABLE 5 - STATE OF IPC DURING RESET

\* If in mode 5, SC1 will go active high; otherwise it will remain in the high impedance state.

\* Mode 0 - \$BFFE, BFFF

Note: Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted.

that this input should have some provision to obtain the specified logical high level which is greater than standard TTL levels.

Enable is the primary IPC system timing signal and all timing data specified as cycles is assumed to be referenced to this clock unless otherwise noted.

### HALT/BUS AVAILABLE/NON-MASKABLE INTERRUPT - HALT/BA/NMI

The HALT/BA/NMI (pin 3) serves one of two functions. These functions are  $\overline{NMI}$  or Halt/BA and the function selected is determined by the Halt Control (HC, bit 2) bit of the Functional Control Register (location \$14). If the HC bit is set (to a '1''), then the  $\overline{NMI}$  function is activated. Alternately, if HC is cleared (to a '0'' as it is during reset), the Halt/BA

function is activated. An external pullup resistor to V<sub>CC</sub> is required on pin 3 for either function. Typical pullup resistor values range from 3K to 10K depending on the drive capability of the external device.

When the  $\overline{NMI}$  function is implemented, pin 3 is configured as an input. A negative edge on pin 3 then requests an IPC non-maskable interrupt sequence, but the current instruction will be completed before responding to this request. To assure an interrupt under all conditions,  $\overline{NMI}$  must be held low for at least one E-cycle.  $\overline{NMI}$  may be used to cause the IPC to exit the Wait instruction. For interrupt timing specifications, see the interrupt portion of the Operating Mode Section.

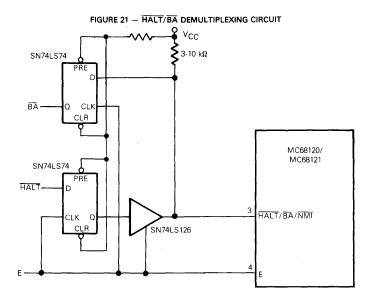

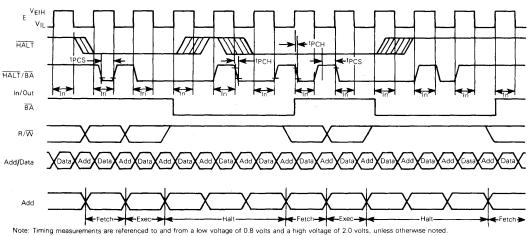

When configured to utilize the Halt/BA function of this pin, such as after reset, the circuit of Figure 21 is recommended to detect and supply continuous  $\overline{HALT}$  and  $\overline{BA}$

signals. Figure 22 shows the appropriate timing diagram for Halt/BA with the recommended circuit. The pullup resistor shown in the circuit maintains a high logic level when HALT is not active. During a positive half-cycle of E, pin 3 is an input sampled to determine if the Halt State is requested (active low). During the negative half cycle of E, the BA signal is detected and the processor completes its current instruction, the CPU is halted and the active low BA signal is output through pin 3 during the negative half cycle of E. The local bus is then available for other devices to utilize until the Halt State signal has returned to a high level, thus allowing the

IPC back on the local bus. During the Halt State, the  $R/\overline{W}$  is high, and the address bus displays the address of the next instruction.

When single instruction operation is desired, in program debug for instance, it is advantageous to single step through instructions. After BA goes low, HALT must be brought high for one E-cycle and returned low again to single step through instructions. Figure 22 illustrates the timing involved while single stepping through a single byte, two bus cycle instruction, such as CLRA.

$\overline{BA}$  is not output in response to the Wait instruction. If interrupts are to be utilized in removing the processor from a

## FIGURE 22 - HALT/BA TIMING DIAGRAM

Wait State while in the Halt/BA mode then,  $\overline{IRQ1}$  and  $\overline{IRQ2}$  are the only interrupts which may do so; therefore, their masks must be cleared before entering the Wait State.

## MASKABLE INTERRUPT REQUEST 1 - IRQ1

This level-sensitive input can be used to request an interrupt sequence. The IPC will complete the current instruction before it responds to the request. If the interrupt mask bit (I-bit) in the Condition Code Register is clear, the IPC will begin an interrupt sequence: a vector is fetched from \$FFF8 and \$FFF9, transferred to the Program Counter, and instruction execution is continued at the new location. This is explained in greater detail in the Interrupt Section.

$\overline{IRQ1}$  typically requires an external resistor (3K to 10K depending on external devices drive capability) to V<sub>CC</sub> for wire-OR applications.  $\overline{IRQ1}$  has no internal pullup resistor.

#### STROBE CONTROL 1 AND 2 - SC1 and SC2

The functions of SC1 and SC2 depend on the operating mode. SC1 is configured as an input in all modes except the Expanded Non-Multiplexed Mode, whereas SC2 is always an output. SC1 and SC2 can drive one Schottky load and 90 pF.

Single Chip Modes – In these modes, SC1 and SC2 are configured as an input and output, respectively, and both function as Port 3 control lines. SC1 functions as an input strobe (IS3) and can be used to indicate that Port 3 input data is ready or output data has been accepted. Three options associated with  $\overline{IS3}$  are controlled by the Control and Status Register for Port 3 and are discussed in the Port 3 description.

SC2 is configured as an output strobe ( $\overline{OS3}$ ) and can be used to strobe output data or acknowledge input data for Port 3. It is controlled by Output Strobe Select (OSS) in the Port 3 Control and Status Register. The strobe is generated by a read (OSS = 0) or write (OSS = 1) to the Port 3 Data Register.  $\overline{OS3}$  timing is shown in Figure 6.

Expanded Non-Multiplexed Mode – In this mode, both SC1 and SC2 are configured as outputs. SC1 functions as Input/Output Select (IOS) and is asserted (active-low) only when addresses \$0100 through \$01FF are accessed. SC2 is configured as  $R/\overline{W}$  and is used to control the direction of local data bus transfers. An MPU read is enabled when  $R/\overline{W}$  and E are high.

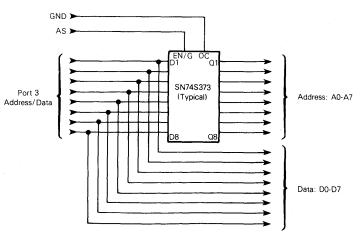

Expanded Multiplexed Modes — In these modes, SC1 is configured as an input and SC2 is configured as an output. In the expanded multiplexed modes, the IPC has the ability to access a 64K byte address space. SC1 functions as an input, Address Strobe, which controls demultiplexing and enabling of the eight least significant addresses and the data buses.

By using a transparent latch such as an SN74LS373 or MC6882, Address Strobe (AS) can also be used to demultiplex the two buses external to the IPC. (See Figure 23.) SC2 provides the local Data Bus control signal called Read/Write (R/W). SC2 is configured as R/W and is used to control the direction of local data bus transfers. An MPU read is enabled when R/W and E are high.

## SYSTEM BUS INTERFACE

Port 1 is a mode-independent 8-bit data port which permits the external system bus to access the dual-ported RAM and semaphore registers either asynchronously or synchronously with respect to the E clock. In addition to the eight data lines (SD0-SD7), eight address (SA0-SA7) and three control lines (SR/W, CS, DTACK) are used to access the dual-ported RAM and semaphore registers.

Port 1 Data Lines (SD0-SD7) — These data lines are bidirectional data lines which allow data transfer between the dual-ported RAM or the semaphore registers, and the system bus. The data bus output drivers are three-state devices which remain in the high-impedance state except

FIGURE 23 - TYPICAL LATCH ARRANGEMENT

during a read of the IPC dual-ported RAM or semaphore registers by the system processor.

System Address Lines (SA0-SA7) – The address lines together with the Chip Select signal allow any of the 128 bytes of RAM or six semaphore registers to be uniquely selected from the system bus. The address lines must be valid before the  $\overline{\rm CS}$  signal goes low for the asynchronous interface and valid before the E signal goes high for the synchronous interface. The system interface must be deselected between reads or between writes for the asynchronous operation.

System Read/Write (SR/ $\overline{W}$ ) — This signal is generated by the system bus to control the direction of data transfer on the data bus. With the IPC selected, a low on the SR/ $\overline{W}$  line enables the input buffers, and data is transferred from the system processor to the IPC. When SR/ $\overline{W}$  is high and the chip is selected, the data output buffers are turned on and data is transferred from the IPC to the system bus.

Chip Select ( $\overline{CS}$ ) — This signal is a TTL compatible input signal, used to activate the system bus interface and allows transfer of data between the IPC and the system processor during synchronous or asynchronous accesses.  $\overline{CS}$  provides the synchronizing signal for the Semaphore registers during access by the system bus.

Data Transfer Acknowledge (DTACK) — This bidirectional control line is used to determine synchronous or asynchronous system bus accesses and to provide the data acknowledge signal for asynchronous data transfers.

As an input, it is sampled on the falling edge of  $\overline{CS}$  by the IPC to determine if the system bus is being accessed synchronously or asynchronously with respect to the E clock.

If DTACK is low when sampled, the system bus is synchronous and data will be transferred during E high as shown in Figure 13.

If DTACK is high when sampled, the system bus is asynchronous. In this mode DTACK becomes an output that is asserted low when data is on the bus during a system read or when a data transfer is completed during a system write. Refer to Figures 9 through 12.

DTACK requires an external pullup resistor when the system bus is run asynchronously since it is then a bidirectional handshake line for information transfer on the system data bus.

## PORT 2 - P20-P24

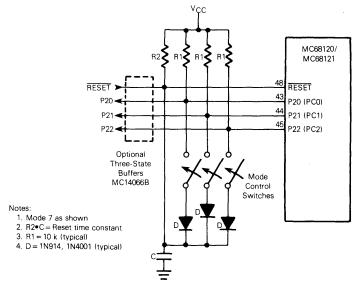

Port 2 is a mode independent 5-bit I/O port where each line is configured by its Data Direction Register. During reset, all lines are configured as inputs. The TTL compatible three-state output buffers can drive one Schottky TTL load and 30 pF, or CMOS devices using external pullup resistors. P20, P21 and P22 must always be connected to provide the operating mode.

|     |     | P   | ORT 2 | DATA | REGIS | STER |     |      |

|-----|-----|-----|-------|------|-------|------|-----|------|

| 7   | 6   | 5   | 4     | 3    | 2     | 1    | 0   |      |

| PC2 | PC1 | PC0 | P24   | P23  | P22   | P21  | P20 | \$03 |

Inputs on P20, P21 and P22 determine the operating mode which is latched into the Program Control Register on the positive edge of RESET. The mode may be read from the Port 2 Data Register (PC2 is latched from pin 45).

Port 2 also provides an interface for the Serial Communications Interface and Timer. Bit 1, if configured as an output, is dedicated to the Timer Output Compare function and cannot be used to provide output from the Port 2 Data Register.

#### PORT 3 - P30-P37

Port 3 can be configured as an I/O port, a bi-directional 8-bit data bus, or a multiplexed address/data bus depending upon the operating mode. The TTL compatible three-state output buffers can drive one Schottky TTL load and 90 pF.

Single Chip Modes — In these modes, Port 3 is an 8-bit I/O port where each line is configured by the Port 3 Data Direction Register. Associated with Port 3 are two lines,  $\overline{IS3}$  and  $\overline{OS3}$ , which can be used to control Port 3 data transfers.

Three Port 3 options, controlled by the Port 3 Control and Status Register and available only in the Single Chip Modes are: 1) Port 3 input data can be latched using IS3 as a control signal, 2) OS3 can be generated by either an IPC read or write to the Port 3 Data Register, and 3) an IRQ1 interrupt can be enabled by an IS3 negative edge. Port 3 latch timing is shown in Figure 7.

PORT 3 CONTROL AND STATUS REGISTER

| 7    | 6      | 5 | 4   | 3      | 2 | 1 | 0 |      |

|------|--------|---|-----|--------|---|---|---|------|

| 153  | IS3    | Х | OSS | LATCH  | Х | Х | Х | \$0F |

| FLAG | IRQ1   |   |     | ENABLE |   |   |   |      |

|      | ENABLE |   |     |        |   |   |   |      |

Bits 0-2 Not used.

- Bit 3 LATCH ENABLE. This bit controls the input latch for Port 3. If set, input data is latched by an IS3 negative edge. The latch is transparent after a read of the Port 3 Data Register. LATCH ENABLE is cleared by Reset.

- Bit 4 OSS (Output Strobe Select). This bit determines whether OS3 will be generated by a read or write of the Port 3 Data Register. When clear, the strobe is generated by a read; when set, it is generated by a write. OSS is cleared by Reset.

- Bit 5 Not used.

- Bit 6 IS3-IRO1 ENABLE. When set, an IRO1 interrupt will be enabled whenever IS3 FLAG is set; when clear, the interrupt is inhibited. This bit is cleared by Reset.

- Bit 7 IS3 FLAG. This read-only status bit is set by an IS3 negative edge. It is cleared by a read of the Port 3 Control and Status Register (with IS3 FLAG set) followed by a read or write to the Port 3 Data Register or by Reset.

Expanded Non-Multiplexed Mode — In this mode, Port 3 is configured as a bi-directional data bus (D0-D7). The direction of data transfers is controlled by  $R/\overline{W}$  (SC2). Data transfers are clocked by E (Enable).

Expanded Multiplexed Modes — In these modes, Port 3 is configured as a time-multiplexed address (A0-A7) and data bus (D0-D7). Address Strobe (AS) must be input on SC1, and can be used externally to de-multiplex the two buses. Port 3 is held in a high-impedance state between valid address and data to prevent potential bus conflicts.

### PORT 4 - P40-P47

Port 4 is configured as 8-bit I/O port, as address outputs, or as data inputs depending on the operating mode. Port 4 can drive one Schottky TTL load and 90 pF and is the only port with internal pullup resistors.

Single Chip Modes — In these modes, Port 4 functions as an 8-bit I/O port where each line is configured by the Port 4 Data Direction Register. Internal pullup resistors allow the port to directly interface with CMOS at 5 volt levels. External

pullup resistors to more than 5 volts, however, cannot be used.

**Expanded Non-Multiplexed Mode** — In this mode, Port 4 is configured from reset as an 8-bit input port, where the Data Direction Register can be written, to provide any or all of address lines A0-A7. Internal pullup resistors are intended to pull the lines high until the Data Direction Register is configured.

Expanded Multiplexed Mode — In all these modes except Mode 6, Port 4 functions as half of the address bus and provides A8 to A15. In Mode 6, the port is configured from reset as an 8-bit parallel input port; the Port 4 Data-Direction Register must be written to provide any or all of address lines, A8 to A15. Internal pullup resistors are intended to pull the lines high until the Data Direction Register is configured (bit 0 controls A8, etc.).

## **OPERATING MODES**

The IPC provides eight different operating modes which are selectable by hardware programming and referred to as Modes 0 through 7. The operating mode controls the memory map, configuration of Port 3, Port 4, SC1 and SC2 and the address location of the interrupt vectors.

## FUNDAMENTAL MODES

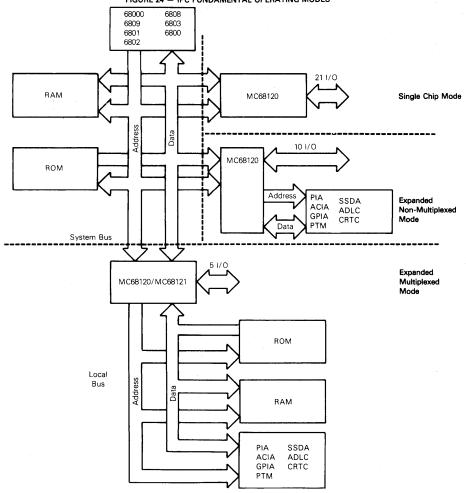

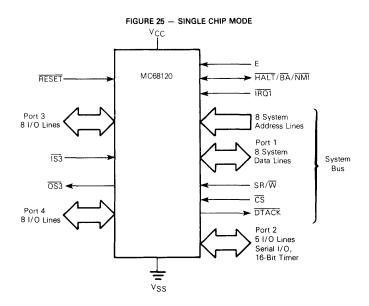

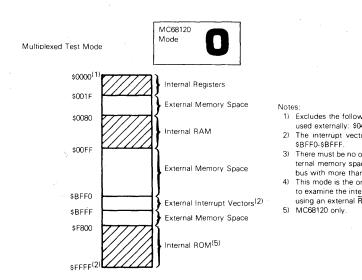

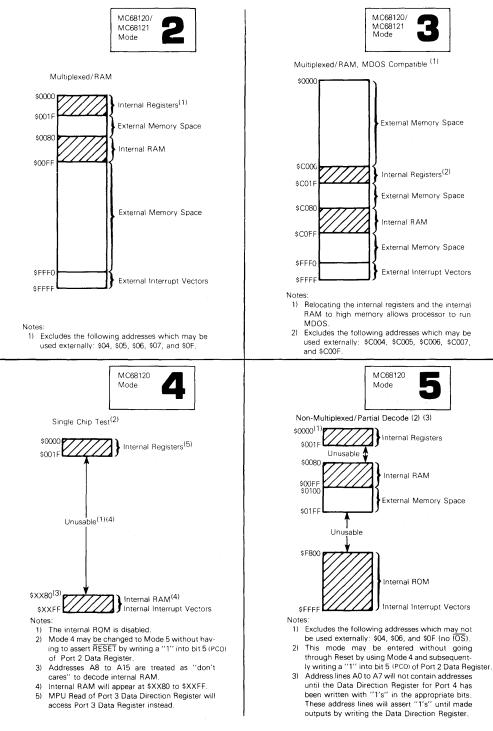

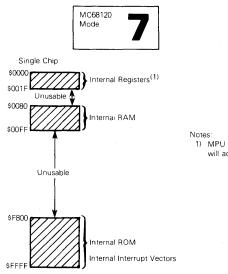

The eight modes of the IPC can be grouped into three fundamental modes which refer to the type of bus it supports: Single Chip, Expanded Non-Multiplexed, and Expanded Multiplexed. Single Chip includes Modes 4 and 7, Expanded Non-Multiplexed is Mode 5 and the remaining five are Expanded Multiplexed modes. A system utilizing three MC68120's, one in each of the fundamental operating modes, is shown in Figure 24. Table 6 summarizes the characteristics of the operating modes. Single Chip Modes (4, 7) — In Single Chip Mode, three of the four IPC ports are configured as parallel input/output data ports, as shown in Figure 25. The IPC functions as a complete microcomputer in these two modes without external address or data buses. A maximum of 21 I/O lines and two Port 3 control lines are provided.

In Single Chip Test Mode (4), the RAM responds to addresses \$XX80 (X = don't care) through \$XXFF and the ROM is removed from the internal address map. A test program must first be loaded into the RAM using Modes 0, 1, 2, or 6. If the IPC is reset and then programmed into Mode 4, execution will begin at \$XXFE:XXFF. Mode 5 can be irreversibly entered from Mode 4 without going through reset by setting bit 5 of the Port 2 Data Register. This mode is used primarily to test Port 3 and 4 in the Single Chip and Non-Multiplexed Modes.

| Common to all Modes:<br>System Bus Interface<br>Reserved Register Area<br>6 Semaphore Registers<br>1/O Port 2<br>Programmable Timer<br>Serial Communications Interface<br>128 bytes of Dual Ported RAM | Expanded Multiplexed Modes<br>Four Memory Space Options (64K Address Space):<br>(1) MDOS Compatible<br>(2) No ROM<br>(3) External Vector Space<br>(4) ROM with Partial Address Bus*<br>External Memory Space Accessed Through:<br>Port 3 as a Multiplexed Address/Data Bus |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single Chip Mode*<br>2048 Bytes of ROM (Internal)<br>Port 3 is a Parallel I/O Port with Two Control Lines<br>Port 4 is a Parallel I/O Port                                                             | Port 4 as an Address Bus (High)<br>SC1 is Address Strobe Bus (AS) Input<br>SC2 is Read/Write (R/W)                                                                                                                                                                         |

| SC1 is Input Strobe 3 (IS3)<br>SC2 is Output Strobe 3 (OS3)                                                                                                                                            | Test Modes<br>Expanded Multiplexed Test Mode<br>May be Used to Test RAM and ROM*                                                                                                                                                                                           |

| Expanded Non-Multiplexed Mode*<br>2048 Bytes of ROM (Internal)<br>256 Bytes of External Memory Space<br>Port 3 is an 8-Bit Data Bus                                                                    | Single Chip and Non-Multiplexed Test Mode*<br>May be Used to Test Ports 3 and 4 as I/O Ports                                                                                                                                                                               |

| Port 3 is an Address Bus<br>SC1 is Input/Output Select (IOS)<br>SC2 is Read/Write (R/W)                                                                                                                | * MC68120 only                                                                                                                                                                                                                                                             |

TABLE 6 - SUMMARY OF IPC OPERATING MODES

FIGURE 24 - IPC FUNDAMENTAL OPERATING MODES

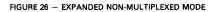

**Expanded Non-Multiplexed Mode (5)** — A modest amount of external memory space is provided in the Expanded Non-Multiplexed Mode while retaining significant on-chip resources. Port 3 functions as an 8-bit bi-directional data bus and Port 4 is configured as an input data port. Any combination of A0 to A7 may be provided while retaining the remainder as input data lines. Any combination of the eight least-significant address lines may be obtained by writing to the Port 4 Data Direction Register. Internal pullup resistors are provided to pull Port 4 lines high until it is configured.

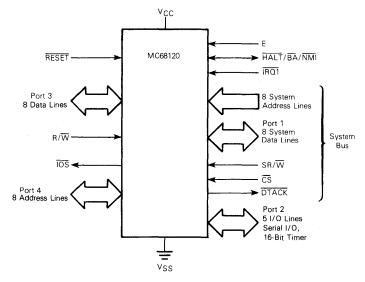

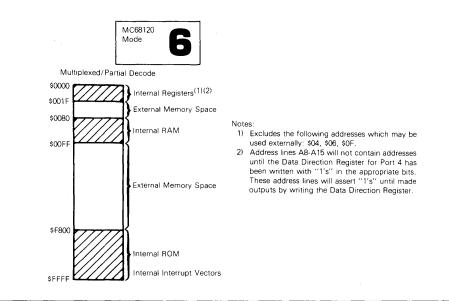

Figure 26 illustrates the external resources available in the Expanded Non-Multiplexed Mode. The IPC interfaces directly with M6800 Family parts and can access 256 bytes of external address space at \$100 through \$1FF. IOS provides an address decode of external memory (\$100-\$1FF) and may be used as an address or chip select line. Expanded-Multiplexed Modes (0, 1, 2, 3, 6) — In the Expanded Multiplexed Modes, the IPC has the ability to access a 64K-byte memory space. Port 3 functions as a time-multiplexed address/data bus with address valid on the negative edge of Address Strobe (AS) and the data bus valid while E is high. In Modes 0 to 3, Port 4 provides address lines A8-A15. However, in Mode 6, Port 4 can provide any subset of A8 to A15 while retaining the remainder as input lines. Writing 1's to the desired bits in the Data Direction Register (DDR) will output the corresponding address lines while the remaining bits will remain inputs (as configured from reset or from 0's written to the DDR). Internal pullup resistors are provided to pull Port 4 lines high until software configures the port. Initialization of Port 4 in Mode six must be done to obtain any upper address lines externally.

3

Figure 27 depicts the external resources available in the Expanded-Multiplexed Modes. Address Strobe can be used to control a transparent D-type latch to capture addresses A0-A7, as shown in Figure 23. This allows Port 3 to function as a Data Bus when E is high.

after the positive edge of RESET. In addition, the internal and external data buses are connected together so there must be no memory map overlap (to avoid potential bus conflicts). Mode 0 is used primarily to verify the ROM pattern and monitor the internal data bus with automated test equipment.

In Mode 0, the reset vector is external at \$BFFE and \$BFFF

### MODE PROGRAMMING

The operating mode is programmed by the levels asserted on P22, P21, and P20 during the positive edge of RESET. These are latched into PC2, PC1, and PC0 of the program control register. The operating mode may be read from the Port 2 Data Register and programming levels and timing must be met as shown in Figure 28 and Table 7. Any mode may be entered from either Mode 0 or Mode 4 without going through reset by writing the appropriate bits to the port 2 data register. A brief outline of the operating modes is shown in Table 8.

Circuitry to provide the programming levels is primarily dependent on the normal system use of the three pins. If

configured as outputs, the circuit shown in Figure 29 may be used; otherwise, the three-state buffers can be used to provide isolation while programming the mode.

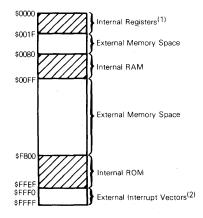

#### MEMORY MAPS

The IPC provides up to 64K bytes of address space depending upon the operating mode. A memory map for each operating mode is shown in Figure 30. In Modes 1R and 6R, the "R" means the ROM has been relocated by a mask option. The first 32 locations of each map are reserved for the IPC internal register area, as shown in Table 9, with exceptions as indicated.

## FIGURE 28 - MODE PROGRAMMING TIMING

| Characteristic                                           | Symbol           | Min | Тур | Max | Unit     |

|----------------------------------------------------------|------------------|-----|-----|-----|----------|

| Mode Programming Input Voltage Low                       | VMPL             | _   | -   | 1.8 | V        |

| Mode Programming Input Voltage High                      | VMPH             | 4.0 | -   | -   | V        |

| Mode Programming Diode Differential (if Diodes are Used) | VMPDD            | 0.6 | -   |     | V        |

| RESET Low Pulse Width                                    | PWRSTL           | 3.0 | _   | -   | E-Cycles |

| Mode Programming Setup Time                              | <sup>t</sup> MPS | 2.0 |     | - 1 | E-Cycles |

| Mode Programming Hold Time                               |                  |     |     |     |          |

| RESET Rise Time≥1 μs                                     | <sup>t</sup> MPH | 0   | -   | -   | ns       |

| RESET Rise Time < 1 µs                                   |                  | 100 | -   | -   | l        |

## TABLE 7 -- MODE PROGRAMMING SPECIFICATIONS (See Figure 30)

## TABLE 8 - MODE SELECTION SUMMARY

| Mode | Pin 45<br>P22<br>PC2 | Pin 44<br>P21<br>PC1 | Pin 43<br>P20<br>PC0 | ROM            | RAM  | Interrupt<br>Vectors | Bus<br>Mode            | Operating<br>Mode                             |

|------|----------------------|----------------------|----------------------|----------------|------|----------------------|------------------------|-----------------------------------------------|

| 7    | н                    | н                    | н                    | I              | 1    | 1                    | 1                      | Single Chip                                   |

| 6    | н                    | н                    | L                    | L L            |      | 1                    | MUX <sup>(5, 6)</sup>  | Multiplexed/Partial Decode <sup>(5)</sup>     |

| 5    | н                    | L                    | н                    | 1              | I    | 1                    | NMUX <sup>(5, 6)</sup> | Non-Multiplexed/Partial Decode <sup>(5)</sup> |

| 4    | н                    | L                    | L                    | <sup>(2)</sup> | l(1) | 1                    | 1                      | Single Chip Test                              |

| 3    | L                    | н                    | н                    | E              | (7)  | E                    | MUX <sup>(4)</sup>     | Multiplexed/RAM <sup>(4)</sup>                |

| 2    | L                    | н                    | L                    | E              | I    | E                    | MUX <sup>(4)</sup>     | Multiplexed/RAM <sup>(4)</sup>                |

| 1    | L                    | L                    | н                    | I              | 1    | E                    | MUX <sup>(4)</sup>     | Multiplexed/RAM and ROM <sup>(4)</sup>        |

| 0    | L                    | L                    | L                    | I              | I I  | E <sup>(3)</sup>     | MUX <sup>(4)</sup>     | Multiplexed Test <sup>(4)</sup>               |

Legend:

I – Internal E – External MUX - Multiplexed NMUX - Non-Multiplexed L - Logic "0" H - Logic "1"

(1) Internal RAM is addressed at \$XX80

(2) Internal ROM is disabled

Notes:

(3) Interrupt vectors externally located at \$BFF0-\$BFFF

(4) Addresses associated with Ports 3 and 4 are considered external in Modes 0, 1, 2, and 3

(5) Addresses associated with Port 3 are considered external in Modes 5 and 6

(6) Port 4 default is user data input; address output is optional by writing to Port 4 Data Direction Register

(7) Internal RAM and registers located at \$C0XX (for use with MDOS)

## FIGURE 29 - TYPICAL MODE PROGRAMMING CIRCUIT

#### FIGURE 30 - IPC MEMORY MAPS

- Excludes the following addresses which may be used externally: \$04, \$05, \$06, \$07 and \$0F.

- The interrupt vectors are externally located at sBEE0-sBEEF

- There must be no overlapping of internal and external memory spaces to avoid driving the data bus with more than one device.

- This mode is the only mode which may be used to examine the interrupt vectors in internal ROM using an external RESET vector.

Multiplexed/RAM and ROM

#### Notes:

- Excludes the following addresses which may be used externally: \$04, \$05, \$06, \$07 and \$0F.

- Internal ROM addresses \$FFF0 to \$FFFF are not usable.

## FIGURE 30 - IPC MEMORY MAPS (CONTINUED)

## FIGURE 30 - IPC MEMORY MAPS (CONCLUDED)

MPU reads of Port 3's Data Direction Register will access Port 3's Data Register instead.

3

| TABLE 9 — INTERNAL REGISTER AREA | TABLE 9 - | INTERNAL | REGISTER AREA |  |

|----------------------------------|-----------|----------|---------------|--|

|----------------------------------|-----------|----------|---------------|--|

| Register                             | Address * * * *<br>(Hexadecimal) | Register                                     | Address****<br>(Hexadecimal) |

|--------------------------------------|----------------------------------|----------------------------------------------|------------------------------|

| Reserved                             | 00                               | SCI Rate and Mode Control Register           | 10                           |

| Port 2 Data Direction Register* * *  | 01                               | Transmit/Receive Control and Status Register | 11                           |

| Reserved                             | 02                               | SCI Receive Data Register                    | 12                           |

| Port 2 Data Register                 | 03                               | SCI Transmit Data Register                   | 13                           |

| Port 3 Data Direction Register * * * | 04*                              |                                              |                              |

| Port 4 Data Direction Register* * *  | 05**                             | Function Control Register                    | 14                           |

| Port 3 Data Register                 | 06*                              | Counter Alternate Address (High Byte)        | 15                           |

| Port 4 Data Register                 | 07 * *                           | Counter Alternate Address (Low Byte)         | 16                           |

| Timer Control and Status Register    | 08                               | Semaphore 1                                  | 17                           |

| Counter (High Byte)                  | 09                               | Semaphore 2                                  | 18                           |

| Counter (Low Byte)                   | 0A                               | Semaphore 3                                  | 19                           |

| Output Compare Register (High Byte)  | 0B                               | Semaphore 4                                  | 1A                           |

| Output Compare Register (Low Byte)   | OC                               | Semaphore 5                                  | 1B                           |

| Input Capture Register (High Byte)   | 0D                               | Semaphore 6                                  | 1C                           |

| Input Capture Register (Low Byte)    | OE                               | Reserved                                     | 1D-1F                        |

| Port 3 Control and Status Register   | OF*                              |                                              |                              |

\*These external addresses in Modes 0, 1, 2, 3, 5, 6 cannot be accessed in Mode 5 (no IOS).

\*\*These are external addresses in Modes 0, 1, 2, 3.

\* \* \* 1 = Output, 0 = Input

\* \* \* \* These addresses relocated at \$C000-\$C01F in Mode 3.

INTERRUPTS

The IPC supports two types of interrupt requests: <u>Maskable</u> and Non-Maskable. A Non-Maskable Interrupt (NMI) is always recognized and acted upon at the completion of the current instruction. Maskable interrupts are controlled by the Condition Code Register I-bit and by individual enable bits. The I-bit controls all maskable interrupts. Of the maskable interrupts, there are two types: IRQ1 and IRQ2. The Programmable Timer and Serial Communications Interface use an internal IRQ2 interrupt line, as shown in the block diagram of the IPC. External devices (and ISQ) use IRQ1. An IRQ1 interrupt is serviced before an IRQ2 interrupt if both are pending.

All IRO2 interrupts use hardware prioritized vectors. The

single SCI interrupt and three timer interrupts are serviced in a prioritized order where each is vectored to a separate location. All IPC vector locations are shown in Table 10, from highest (top) to lowest (bottom) priority.

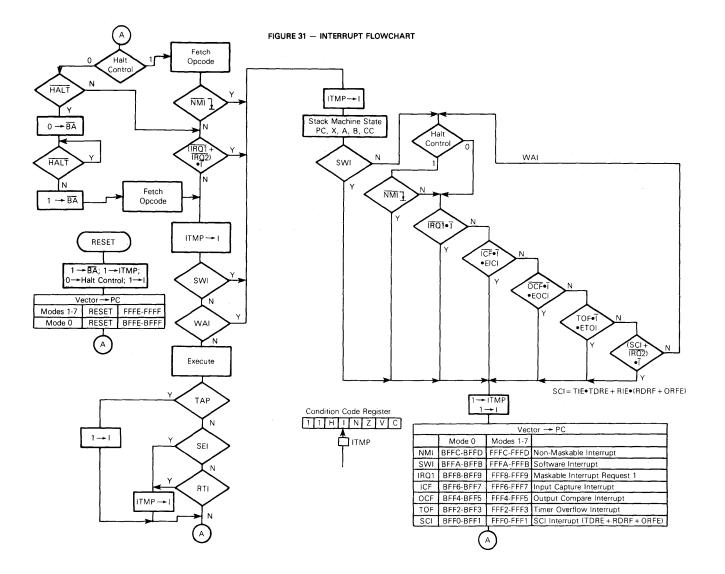

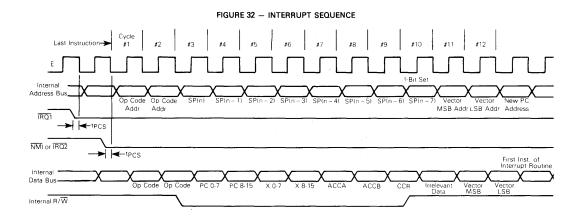

The interrupt flowchart is depicted in Figure 31. The Program Counter, Index Register, Accumulator A, Accumulator B, and Condition Code Register are pushed to the stack. The I-bit is set to inhibit maskable interrupts and a vector is fetched corresponding to the current highest priority interrupt. The vector is transferred to the Program Counter and instruction execution is resumed. The general interrupt timing sequence is shown in Figure 32. The Interrupt HALT/BA timing is illustrated in Figure 21 and 22.

| MSB    | LSB  | Interrupt                |

|--------|------|--------------------------|

| \$FFFE | FFFF | RESET * *                |

| FFFC   | FFFD | NMI                      |

| FFFA   | FFFB | Software Interrupt (SWI) |

| FFF8   | FFF9 | IRQ1 (or IS3)            |

| FFF6   | FFF7 | ICF (Input Capture)      |

| FFF4   | FFF5 | OCF (Output Compare)     |

| FFF2   | FFF3 | TOF (Timer Overflow)     |

| FFFO   | FFF1 | SCI (RDRF + ORFE + TDRE) |

#### TABLE 10 - MCU VECTOR LOCATIONS \*

\*These locations are relocated at \$BFF0-\$BFFF in Mode 0.

\* \* Highest priority.

ω

MC68120, MC68121

#### PROGRAMMABLE TIMER

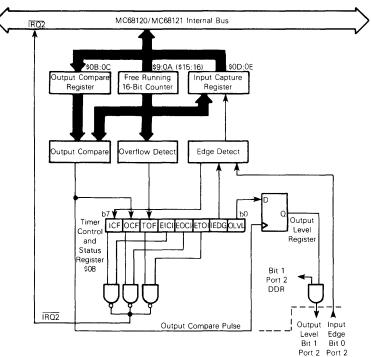

The Programmable Timer can be used to perform input waveform measurements while independently generating an output waveform. Pulse widths can vary from several microseconds to many seconds. A block diagram of the Timer is shown in Figure 33.

#### TIMER CONTROL AND STATUS REGISTER (\$08)

The Timer Control and Status Register (TCSR) is an 8-bit register of which all bits are readable while bits 0-4 can be written. The three most significant bits provide the timer status and they indicate:

- a proper level transition has been detected, or

- a match has been found between the free-running

- counter and the output compare register, or

- the free-running counter has overflowed.

Each of the three events can generate an IRO2 interrupt and is controlled by an individual enable bit in the TCSR.

TIMER CONTROL AND STATUS REGISTER

|     |     |     | ``   | 100117 |      |      |      |      |

|-----|-----|-----|------|--------|------|------|------|------|

| 7   | 6   | 5   | 4    | 3      | 2    | 1    | 0    |      |

| ICF | OCF | TOF | EICI | EOCI   | ETOI | IEDG | OLVL | \$08 |

- Bit 0 OLVL Output level. OLVL is clocked to the output level register by a successful output compare and will appear at P21 if Bit 1 of the Port 2 Data Direction Register is set. It is cleared by reset.

- Bit 1 IEDG Input Edge. IEDG is cleared by reset and controls which level transition will trigger a counter transfer to the Input Capture Register: IEDG = 0 Transfer on a negative edge IEDG = 1 Transfer on a positive edge

- Bit 2 ETOI Enable Timer Overflow Interrupt. When set, an IRO2 interrupt is enabled for a timer overflow;

when clear, the interrupt is inhibited. It is cleared by reset.

- Bit 3 EOCI Enable Output Compare Interrupt. When set, an IRO2 interrupt is enabled for an output compare; when clear, the interrupt is inhibited. It is cleared by reset.

- Bit 4 EICI Enable Input Capture Interrupt. When set, an IRQ2 interrupt is enabled for an input capture; when clear, the interrupt is inhibited. It is cleared by reset.

- Bit 5 TOF Timer Overflow Flag. TOF is set when the counter contains all 1's. It is cleared by reading the TCSR (with TOF set) followed by reading the highest byte of the counter (\$09), or by reset. Reading the counter at \$15 will not clear TOF.

- Bit 6 OCF Output Compare Flag. OCF is set when the Output Compare Register matches the free-running counter. It is cleared by reading the TCSR (with OCF set) and then writing to the Output Compare Register (\$0B or \$0C), or by reset.

- Bit 7 ICF Input Capture Flag. ICF is set to indicate a proper level transition. It is cleared by reading the TCSR (with ICF set) and then reading the Input Capture Register High Byte (\$0D), or by reset.

## COUNTER (\$09:0A)

The key timer element is a 16-bit free-running counter which is incremented by E (Enable). It is cleared during reset and is a read-only with one exception: a write to the counter (509) will preset it to \$FFF8. This feature, intended for testing, can disturb serial operations because the counter provides the SCI internal bit rate clock. TOF is set whenever the counter contains all 1's. The counter may also be read at location \$15 and \$16 to avoid the clearing of the TOF.

FIGURE 33 -- PROGRAMMABLE TIMER -- BLOCK DIAGRAM

#### OUTPUT COMPARE REGISTER (\$0B:0C)

The Output Compare Register is a 16-bit Read/Write register used to control an output waveform or provide an arbitrary timeout flag. It is compared with the free-running counter on each E-cycle. When a match is found, OCF is set and OLVL is clocked to an output level register. If Port 2, bit 1 is configured as an output, OLVL will appear at P21. The Output Compare Register and OLVL can then be changed for the next compare. The compare function is inhibited for one cycle after a write to the high byte of the counter (\$08) to ensure a valid compare. The Output Compare Register is set to \$FFFF by reset.

#### INPUT CAPTURE REGISTER (\$0D:0E)

The Input Capture Register is a 16-bit read-only register used to store the free-running counter when a "proper" input transition occurs as defined by IEDG. Port 2, bit 0 should be configured as an input, but the edge detect circuit always senses P20, even when configured as an output. An input capture can occur independently of ICF: the input capture register always contains the most current value regardless of whether ICF was previously set or not. Counter transfer is inhibited, however, between accesses of a double byte IPC read. The input pulse width must be at least two E-cycles to ensure an input capture under all conditions.

## SERIAL COMMUNICATIONS INTERFACE (SCI)

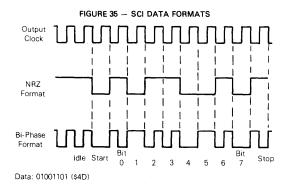

A full-duplex asynchronous Serial Communications Interface (SCI) is provided with two data formats and a choice of Baud rates. The SCI transmitter and receiver are functionally independent, but use the same data format and bit rate. Serial data formats include standard mark/space (NRZ) and Bi-phase. Both formats provide one start bit, eight data bits, and one stop bit. "Baud" and "bit rate" are used synonymously in the following description.

#### WAKE-UP FEATURE

In a typical serial loop multi-processor configuration, the software protocol will usually identify the addressee(s) at the

beginning of the message. In order to allow uninterested MPUs to ignore the remainder of the message, a wake-up feature is included whereby all further SCI receiver flag (and interrupt) processing can be inhibited until the data line goes idle. An SCI receiver is re-enabled by an idle string of ten consecutive 1's or by reset. Software must provide the required idle string between consecutive messages and prevent it within messages.

## PROGRAMMABLE OPTIONS

- The following features of the SCI are programmable:

- format: standard mark/space (NRZ) or Bi-phase

- · clock: external or internal clock source

- Baud rate: one of four per E-clock frequency, or oneeighth of the external clock input to P22

- wake-up features: enabled or disabled

- interrupt requests: enabled individually for transmitter and receiver

- clock output: internal bit rate clock enabled or disabled to P22

#### SERIAL COMMUNICATIONS REGISTERS

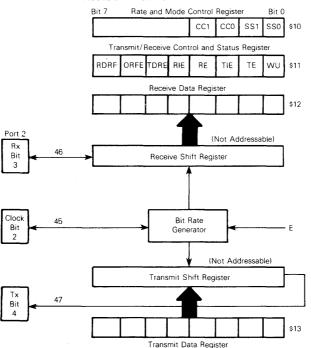

The Serial Communications Interface includes four addressable registers as depicted in Figure 34. It is controlled by the Rate and Mode Control Register and the Transmit/Receive Control and Status Register. Data is transmitted and received utilizing a write-only Transmit Register and read-only Receive Register. The shift registers are not accessible by software.

Rate and Mode Control Register (\$10) — The Rate and Mode Control Register (RMCR) controls the SCI Baud rate, format, clock source, and under certain conditions, the configuration of P22. The register consists of four write-only bits which are cleared by reset. The two least significant bits control the Baud rate of the internal clock and the remaining two bits control the format and clock source. RATE AND MODE CONTROL REGISTER (RMCR)

| X X X X CC1 CC0 SS1 SS0 \$1 | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |      |

|-----------------------------|---|---|---|---|-----|-----|-----|-----|------|

|                             | Х | Х | Х | Х | CC1 | CC0 | SS1 | SS0 | \$10 |

- Bit 1: Bit 0 SS1:SS0 Speed Select. These two bits select the Baud rate when using the internal clock. Four rates may be selected which are a function of the IPC input frequency (E). Table 11 lists bit times and rates for three selected IPC frequencies.